#### GW8316

## 6-Channel Proximity Sensor for SAR Applications

## 1 Description

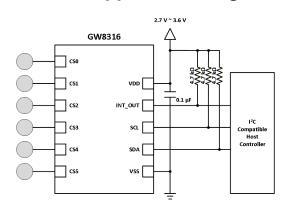

The GW8316 is an advanced 6-channel capacitive sensor MCU designed specifically for SAR (Specific Absorption Rate) applications. Capable of high-performance proximity detection based on capacitive sensing circuit operating with a wide range 2.7 V  $\sim$  3.6 V supply voltage, this intelligent and smart sensor excels the presence detection of a user at various distances. With the human body proximity detection ability of the GW8316, radio frequency (RF) emission power can be optimized in the presence of the human body. The GW8316 provides noticeable performance benefits to portable electronic manufacturers by helping them to comply with stringent electromagnetic radiation regulations and SAR standards.

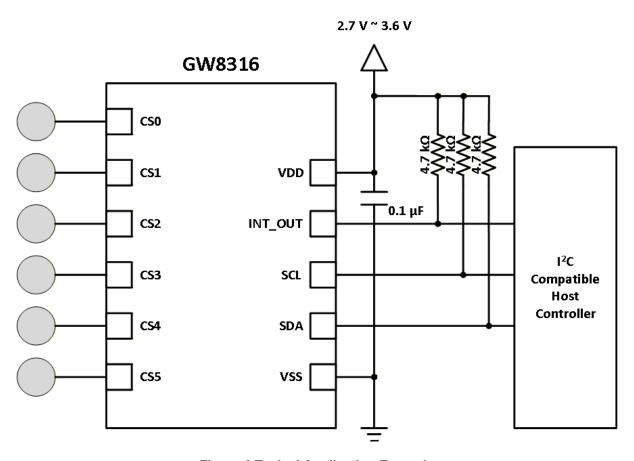

The GW8316 communicates to a host over the Inter-Integrated Circuit( $I^2C$ ) serial bus, which can solely operate even in sleep mode. The Host can wake up the device from sleep mode with an  $I^2C$  command. The interrupt signal output can be activated to allow the host to get the relative proximity distance or to receive a detection notification in an efficient way.

Equipped with an on-chip calibration functionality, the GW8316 can maintain performance across a wide range of temperatures, humidity, and noisy conditions. This feature allows for regular sensitivity adjustments, simplifying product development and improving overall performance.

#### 2 Features

- Flexible 2.7 V ~ 3.6 V supply voltage

- High performance capacitive sensing circuit

- 6 capacitive sensing inputs

- Capacitance resolution: 1 aF

- □ Capacitance offset compensation: ~ 300 pF

- Automatic offset capacitance calibration

- Active shield driver

- Temperature sensor for compensation

- 8051 compatible MCU core

- 32 KB Flash, 3KB SRAM

- Capacitive sensor control interface

- Separate configurations per channel

- Digital sensor status output

- Dedicated digital signal processing core

- Peripherals

- 2 Timer, 1 WDT

- 2 I<sup>2</sup>C serial interfaces, 1 UART

- DMA

- GPIO

- 2 PWM

- External interrupt output

- Flexible Event/Status Handling

- Low power consumption

- Active mode: 50 μA

- Sleep mode: 1.9 μA

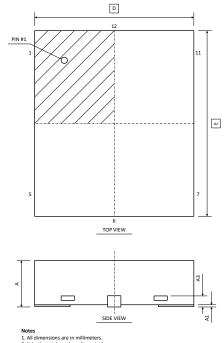

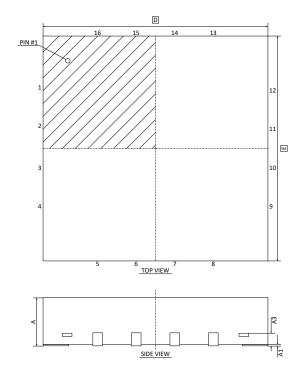

## 3 Physical Characteristics

- Supply voltage:  $2.7 \text{ V} \sim 3.6 \text{ V}$

- Operating temperature: -40 °C ~ 105 °C

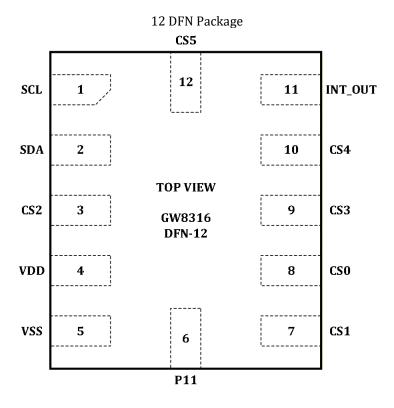

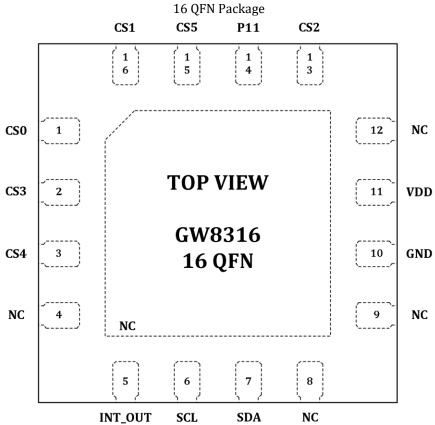

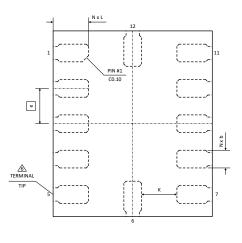

- 12 DFN: 1.8 mm x 2.1 mm, 0.4 mm pitch

- 16 QFN: 3.5 mm x 3.5 mm, 0.8 mm pitch

- Pb & Halogen Free, RoHS/WEEE compliant

## 4 Typical Applications

- Wireless portable devices

- Smartphones/Tablets/Laptops

- Hotspots

- Others

## 5 Basic Application Diagram

# 6 Ordering Information

| Device name  | Package                          | Remark             |

|--------------|----------------------------------|--------------------|

| GW8316ADQDR  | 1.8 mm x 2.1 mm,<br>0.4 mm pitch | 12 DFN<br>Consumer |

| GW8316ARRJRQ | 3.5 mm x 3.5 mm,<br>0.4 mm pitch | 16 QFN<br>AEC-Q100 |

## **Table of Contents**

| 1  | Description |                                         |    | 10.3 | Prox     | ximity Sensing Interface              | 10    |

|----|-------------|-----------------------------------------|----|------|----------|---------------------------------------|-------|

| 2  | Featu       | res1                                    |    |      | 10.3.1   | Introduction                          |       |

| 3  | Physic      | cal Characteristics1                    |    | 10.4 | Ana      | llog Front End (AFE)                  |       |

| _  | -           |                                         |    |      | 10.4.1   | Capacitance Sensing                   | 11    |

| 4  | Typica      | al Applications1                        |    |      | 10.4.2   | CS Input and Active Shield Driver     | 11    |

| 5  | Basic       | Application Diagram1                    |    |      | 10.4.3   | AFE Block Diagram                     | 11    |

| 6  | Order       | ring Information1                       |    |      | 10.4.4   | Capacitance to Voltage Conversion (C- | V)11  |

| 7  |             | _                                       |    |      | 10.4.5   | Capacitance Compensation              | 11    |

| 7  | Revisi      | on History2                             |    |      | 10.4.6   | Analog to Digital Conversion (ADC)    | 11    |

| 8  | Pin Co      | onfiguration and Function3              |    |      | 10.4.7   | Scan Period Controller                | 12    |

| 9  | Specif      | fications5                              |    | 10.5 | Digi     | ital Signal Processing                | 12    |

|    | 9.1         | Absolute Maximum Ratings5               |    | 10.6 | Hos      | t Communication                       | 12    |

|    | 9.2         | Recommended Operating Conditions5       |    | 10.7 | Pow      | ver Controls                          | 13    |

|    | 9.3         | Thermal Characteristics5                |    | 10.8 | $I^2C$   | Interface                             | 14    |

|    | 9.4         | DC Characteristics5                     |    |      | 10.8.1   | Introduction                          | 14    |

|    | 9.5         | Internal DC Regulator Characteristics6  |    | 10.9 | Reg      | isters                                | 14    |

|    | 9.6         | Electrical Characteristics6             | 11 | Арр  | licatior | าร                                    | 31    |

|    | 9.7         | Timing Diagrams7                        |    | 11.1 | Турі     | ical Application                      | 31    |

|    | 9           | 0.7.1 I <sup>2</sup> C Timing Diagrams7 |    | 11.2 | Guid     | delines for external component sele   | ction |

| 10 | Functi      | ional Description9                      |    |      | 31       |                                       |       |

|    | 10.1        | Overview9                               | 12 | Pack | age In   | formation                             | 32    |

|    | 10.2        | Functional Block Diagram9               |    |      |          |                                       |       |

|    |             |                                         |    |      |          |                                       |       |

# 7 Revision History

| Version | Date             | Description     |

|---------|------------------|-----------------|

| 1.0     | December 2, 2025 | Initial release |

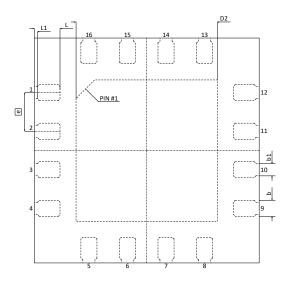

# 8 Pin Configuration and Function

### **Pin Description**

| Pin Name                                   | 12 DFN<br>Pin No. | 16 QFN<br>Pin No. | Туре | Description                                                                                                                                                                          |

|--------------------------------------------|-------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00<br>CS0<br>-                            | 8                 | 1                 | IO   | GPIO: Port0.0 AFE: Capacitive sensor input/Active shield output: channel 0 -                                                                                                         |

| DSDA                                       |                   |                   |      | DBG: Debugger interface, serial data                                                                                                                                                 |

| P06<br>CS3<br>TIMER3_O<br>PWM11_IO/OSCLS_O | 9                 | 2                 | IO   | GPIO: Port0.6 AFE: Capacitive sensor input/Active shield output: channel 3 TIMER3: interrupt output PWM1: PWM Port1, 1st output/input or 128 kHz internal oscillator output          |

| P07<br>CS4<br>UART_RX<br>TIMER1_O/PWM01_IO | 10                | 3                 | IO   | GPIO: Port0.7 AFE: Capacitive sensor input/Active shield output: channel 4 UART: RXD TIMER1: interrupt output or PWM0: PWM Port0, 1st PWM output/input -                             |

| NC                                         | -                 | 4                 | NC   | No connection                                                                                                                                                                        |

| P02<br>XINTO_IN<br>UART_TX<br>INT_OUT      | 11                | 5                 | IO   | GPIO: Port0.2<br>External interrupt 0 input<br>UART: TXD<br>Interrupt events open-drain output, external resistor required                                                           |

| P04<br>SSCL<br>UART_TX<br>SCL0             | 1                 | 6                 | IO   | GPIO: Port0.4  I <sup>2</sup> CS: Serial clock input  UART: TXD  I <sup>2</sup> C0: Serial clock input/output                                                                        |

| P03<br>SSDA<br>UART_RX<br>SDA0             | 2                 | 7                 | IO   | GPIO: Port0.3 I²CS: Serial data input, requires external 4.7 k $\Omega$ pull-up resistor UART: RXD I²CO: Serial data input/output, requires external 4.7 k $\Omega$ pull-up resistor |

| NC                                         | -                 | 8                 | NC   | No connection                                                                                                                                                                        |

| NC                                         | -                 | 9                 | NC   | No connection                                                                                                                                                                        |

| GND                                        | 5                 | 10                | G    | Power ground                                                                                                                                                                         |

| VDD                                        | 4                 | 11                | P    | Power supply; requires decoupling capacitors between VDD and GND                                                                                                                     |

| NC                                         | -                 | 12                | NC   | No connection                                                                                                                                                                        |

| P05<br>CS2<br>SCLK_OUT<br>OSCHS_O<br>-     | 3                 | 13                | IO   | GPIO: Port0.5 AFE: Capacitive sensor input/Active shield output: channel 2 System clock output 16 MHz internal oscillator output -                                                   |

| P11                                        |                   |                   |      | GPIO: Port1.1                                                                                                                                                                        |

| -<br>PWM12_0                               | 6                 | 14                | IO   | -<br>PWM1: PWM Port1, 2 <sup>nd</sup> output                                                                                                                                         |

| -<br>EXCK_EN                               |                   |                   |      | -<br>DBG: External clock input on/off selection, only for debugging                                                                                                                  |

| P10<br>CS5<br>PWM02_0                      | 12                | 15                | IO   | GPIO: Port1.0  AFE: Capacitive sensor input/Active shield output: channel 5  PWM0: PWM port0, 2 <sup>nd</sup> output                                                                 |

| CLK_EXT                                    |                   |                   |      | DBG: External clock input                                                                                                                                                            |

| Pin Name                          | 12 DFN<br>Pin No. | 16 QFN<br>Pin No.    | Type | Description                                                                                                      |

|-----------------------------------|-------------------|----------------------|------|------------------------------------------------------------------------------------------------------------------|

| P01<br>CS1<br>-<br>-<br>-<br>DSCL | 7                 | 16                   | 10   | GPIO: Port0.1 AFE: Capacitive sensor input/Active shield output: channel 1 DBG: Debugger interface, serial clock |

| NC                                | -                 | 17<br>Exposed<br>Pad | NC   | No connection                                                                                                    |

# 9 Specifications

## 9.1 Absolute Maximum Ratings

| Parameter                      | Symbol             | Min   | Max | Unit |

|--------------------------------|--------------------|-------|-----|------|

| Supply Voltage                 | $V_{DD}$           | -0.5  | 5.5 | V    |

| Input Voltage                  | V <sub>IH</sub>    | -0.5  | 5.5 | V    |

| Operating Junction Temperature | T <sub>JCT</sub>   | -40   | 125 | V    |

| Storage temperature            | T <sub>STG</sub>   | -55   | 150 | °C   |

| ESD HBM(ANSI/ESDA/JEDE JS-001) | ESD <sub>HBM</sub> | 8,000 | -   | V    |

## 9.2 Recommended Operating Conditions

| Parameter                     | Symbol         | MIN    | TYP | MAX | UNIT |

|-------------------------------|----------------|--------|-----|-----|------|

| Supply Voltage <sup>(1)</sup> | $V_{DD}$       | 2.7(2) |     | 3.6 | V    |

| Ambient Temperature           | T <sub>A</sub> | -40    |     | 105 | °C   |

<sup>1.</sup>  $I^2C/INT\_OUT$  Pull-up resistors must not exceed the  $V_{DD}$  voltage level.

### 9.3 Thermal Characteristics

| Parameter                                                            | Symbol        | Typical | UNIT |

|----------------------------------------------------------------------|---------------|---------|------|

| Thermal Resistance – Junction to Air (Static Airflow) <sup>(1)</sup> | $\theta_{JA}$ | TBD     | °C/W |

<sup>1.</sup>  $\theta_{JA}$  is derived using a package situated in stationary air and affixed to a 3" x 4.5" 4-layer FR4 PCB, following JESD51 guidelines

### 9.4 DC Characteristics

| Parameter                                               | Symbol              | MIN  | TYP  | MAX      | UNIT |

|---------------------------------------------------------|---------------------|------|------|----------|------|

| Input high voltage                                      | V <sub>IH</sub>     | 2.0  |      | VDDA+0.3 | V    |

| Input high voltage, Schmitt trigger (V <sub>T+</sub> )  | V <sub>IH,SCH</sub> |      |      | 2.1      | V    |

| Input low voltage                                       | V <sub>IL</sub>     | -0.3 |      | 0.8      | V    |

| Input low voltage, Schmitt trigger (V <sub>T-</sub> )   | V <sub>IL,SCH</sub> | 0.7  |      |          | V    |

| Hysteresis (V <sub>T+</sub> – V <sub>T-</sub> )         | V <sub>HYS</sub>    | 0.2  |      | 1.4      | V    |

| Input high current, V <sub>IN</sub> =V <sub>DDA</sub>   | I <sub>IH</sub>     | -10  |      | 10       | μΑ   |

| Input with pull-down, V <sub>IN</sub> =V <sub>DDA</sub> | I <sub>IH,PD</sub>  | 80   | 100  | 125      | μA   |

| Input low current, V <sub>IN</sub> =V <sub>DDA</sub>    | I <sub>IL</sub>     | -10  |      | 10       | μA   |

| Input with pull-up, V <sub>IN</sub> =V <sub>DDA</sub>   | I <sub>IL,PU</sub>  | -80  | -100 | -125     | μΑ   |

<sup>2.</sup> For optimal analog device performance, it is recommended that  $V_{DD}$  be equal to or greater than 2.7V.

| Parameter                      | Symbol          | MIN | TYP | MAX | UNIT |

|--------------------------------|-----------------|-----|-----|-----|------|

| Output high voltage            | V <sub>OH</sub> | 2.4 |     |     | V    |

| Output low voltage             | V <sub>OL</sub> |     |     | 0.4 | V    |

| 3-State output leakage current | l <sub>oz</sub> | -10 |     | 10  | μΑ   |

## 9.5 Internal DC Regulator Characteristics

| Parameter                           | Symbol                   | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------|--------------------------|------|------|------|------|

| Internal digital LDO supply voltage | $V_{DDD}$                | 1.35 | 1.5  | 1.65 | V    |

| Internal digital LDO supply current | I <sub>DDD</sub>         |      |      | 15   | mA   |

| Power on reset lockout voltage      | V <sub>POR,LOCKOUT</sub> |      | 2.13 |      | V    |

| Power on reset release voltage      | V <sub>POR,RELEASE</sub> |      | 2.27 |      | V    |

| Power on reset delay                | $V_{POR,DELAY}$          |      |      | 1.2  | ms   |

## 9.6 Electrical Characteristics

Unless stated otherwise, all values are applicable within the complete range of operational conditions. Typical values are given for  $T_A = +25\,^{\circ}\text{C}$ ,  $V_{DD} = 3.3\,\text{V}$

| Parameter                          | Symbol                  | Conditions                                                                                                                                | MIN    | TYP     | MAX     | UNIT |

|------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|------|

| Power Supply                       |                         |                                                                                                                                           |        |         |         |      |

| Active                             | I <sub>ACTIVE</sub>     | Scan Period = 30 ms Clock Frequency = 200 kHz Oversample = 64 CVC Gain = 4 ADC Gain = 1 DSP Disabled I <sup>2</sup> C listening. No load  |        | 50      |         | μА   |

| Doze                               | I <sub>DOZEI</sub>      | Scan Period = 390 ms Clock Frequency = 200 kHz Oversample = 64 CVC Gain = 4 ADC Gain = 1 DSP Disabled I <sup>2</sup> C listening. No load |        | 8       |         | μΑ   |

| Sleep                              | I <sub>SLEEP</sub>      | Power down I <sup>2</sup> C listening                                                                                                     |        | 1.9     |         | μA   |

| Capacitance to Voltage Co          | nverter (CVC)           | ) + ADC                                                                                                                                   |        |         |         |      |

| Active Current                     | I <sub>ACTIVE</sub>     |                                                                                                                                           |        | 600     |         | μΑ   |

| Power Down Current                 | I <sub>PD</sub>         |                                                                                                                                           |        | 0.2     |         | μΑ   |

| External DC Capacitor to Ground    | C <sub>EXT</sub>        |                                                                                                                                           |        |         | 300     | pF   |

| Input Capacitance Range            | C <sub>RANGE</sub>      |                                                                                                                                           | ±1.05  |         | ±8.1375 | pF   |

| Measurement Range<br>Control Step  | C <sub>RANGE,STEP</sub> |                                                                                                                                           |        | ±0.2625 |         | pF   |

| Offset Cancellation DAC Resolution | N <sub>BIT,DAC</sub>    |                                                                                                                                           |        | 14      |         | Bits |

| CVC/ADC Sampling                   | F <sub>Sampling</sub>   |                                                                                                                                           | 7.8125 | 250     | 500     | kHz  |

| Parameter                             | Symbol                | Conditions                                                                    | MIN | ТҮР  | MAX | UNIT |

|---------------------------------------|-----------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Frequency                             |                       |                                                                               |     |      |     |      |

| ADC Oversampling Ratio                | OSR                   |                                                                               | 1   | 32   | 512 |      |

| Management Decaletion                 | N <sub>BIT</sub>      | C <sub>RANGE</sub> = ±1.05, ADC Gain = 1                                      |     | 21   |     | Bits |

| Measurement Resolution                | C <sub>RES</sub>      | Default Gain                                                                  |     | 1    |     | aF   |

| Output Resolution                     | N <sub>BIT</sub>      | 12 + log <sub>2</sub> (OSR)                                                   | 12  |      | 21  | bits |

| Oscillators                           |                       |                                                                               |     |      |     |      |

| Nominal Oscillator<br>Frequency, Fast | F <sub>OSC,FAST</sub> |                                                                               |     | 16   |     | MHz  |

| Nominal Oscillator<br>Frequency, Slow | F <sub>osc,slow</sub> |                                                                               |     | 128  |     | kHz  |

| Oscillator Trim Step                  | OSC <sub>TRIM</sub>   | Around Nominal Value $T_A = + 25 ^{\circ}\text{C}$ , $V_{DDA} = 3.3 \text{V}$ |     | 0.65 |     | %    |

| Oscillator Temperature Dependency     | OSC <sub>TEMPD</sub>  |                                                                               |     | ±2   |     | %    |

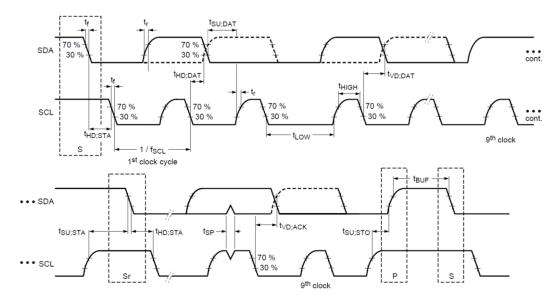

# 9.7 Timing Diagrams

## 9.7.1 I<sup>2</sup>C Timing Diagrams

Figure 1 I<sup>2</sup>C Timing Diagram

Table 1 I<sup>2</sup>C Timing Parameters

| Parameter           | Symbol        | Conditions | MIN | TYP | MAX | UNIT |

|---------------------|---------------|------------|-----|-----|-----|------|

| SCL clock frequency | $t_{\sf SCL}$ |            |     |     | 400 | kHz  |

| Parameter                            | Symbol             | Conditions | MIN                       | TYP | MAX | UNIT |

|--------------------------------------|--------------------|------------|---------------------------|-----|-----|------|

| SCL low period                       | t <sub>LOW</sub>   |            | 1.3                       |     |     | μs   |

| SCL high period                      | t <sub>HIGH</sub>  |            | 0.6                       |     |     | μs   |

| Data setup time                      | t <sub>SUDAT</sub> |            | 0.1                       |     |     | μs   |

| Data hold time                       | t <sub>HDDAT</sub> |            | 0                         |     |     | μs   |

| Repeated start setup time            | t <sub>SUSTA</sub> |            | 0.6                       |     |     | ns   |

| Start condition hold time            | t <sub>HDSTA</sub> |            | 0.6                       |     |     | μs   |

| Stop condition setup time            | t <sub>susto</sub> |            | 0.6                       |     |     | μs   |

| Bus free time between stop and start | t <sub>BUF</sub>   |            | 1.3                       |     |     | μs   |

| Data valid time                      | t <sub>VDDAT</sub> |            |                           |     | 0.9 | μs   |

| Data valid acknowledge time          | t <sub>VDACK</sub> |            |                           |     | 0.9 | μs   |

| Rise time of SCL                     | t <sub>rCL</sub>   |            | 20                        |     | 300 | ns   |

| Fall time of SCL                     | t <sub>fCL</sub>   |            | 20*(V <sub>DD</sub> /5.5) |     | 300 | ns   |

| Rise time of SDA                     | t <sub>rDA</sub>   |            | 20                        |     | 300 | ns   |

| Fall time of SDA                     | t <sub>fDA</sub>   |            | 20*(V <sub>DD</sub> /5.5) |     | 300 | ns   |

| Input glitch suppression             | t <sub>SP</sub>    | See note 1 | 0                         |     | 50  | ns   |

Notes:

$<sup>^{\</sup>rm 1}$  Minimum glitch amplitude is  $0.7V_{\text{DD}}$  at high level and maximum  $0.3V_{\text{DD}}$  at low level

# 10 Functional Description

#### 10.1 Overview

The GW8316 is an advanced 6-channel capacitive sensor MCU for Specific Absorption Rate (SAR) applications. Capable of high-performance proximity detection based on capacitive sensing circuit operating with a wide range  $2.7~V\sim3.6~V$  supply voltage, this intelligent and smart sensor excels the presence detection of a user at various distances. With the human body proximity detection ability of the GW8316, radio frequency (RF) emission power can be optimized in the presence of the human body. The GW8316 provides noticeable performance benefits to portable electronic devices manufacturers by helping them to comply with stringent electromagnetic radiation regulations and SAR standards.

With the GW8316, users can implement fully customized proximity sensing functions such as periodical sensing with environmental variation compensation. Simple register based control structure supports efficient Active Mode/Doze Mode/IDLE Mode implementation for power optimized operations.

Equipped with an on-chip calibration functionality, the GW8316 can maintain performance across a wide range of temperatures, humidity, and noisy conditions. This feature allows for regular sensitivity adjustments, simplifying product development and improving overall performance.

The GW8316 communicates to a host over the Inter-Integrated Circuit (I<sup>2</sup>C) serial bus, which can solely operate even in sleep mode. The host can wake up the device from sleep mode with an I<sup>2</sup>C command. The interrupt signal output (INT\_OUT) can be activated to allow the host to get the relative proximity distance or to receive a detection notification in an efficient way.

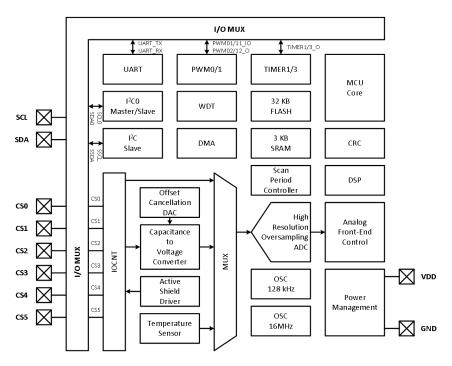

### 10.2 Functional Block Diagram

Figure 2 illustrates the functional block of the GW8316.

Figure 2 Functional Block Diagram

## 10.3 Proximity Sensing Interface

#### 10.3.1 Introduction

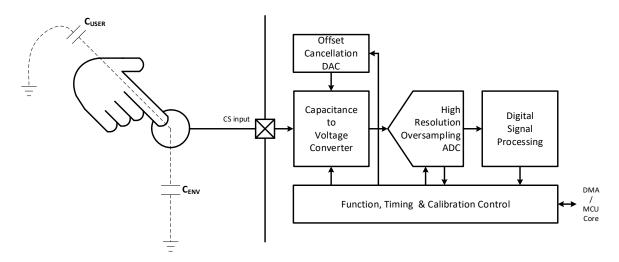

The primary role of the proximity sensing interface is to identify the presence of a conductive object, often a part of the human body like a finger, palm, or face, in close proximity to the system as relative parasitic capacitance changes to the ground. Capacitive proximity sensing is widely used due to its accuracy and versatility. The GW8316 capacitive proximity sensing structure is illustrated in the figure.

**Figure 3 Proximity Sensing Interface**

The sensor could be as straightforward as a copper region on a PCB or FPC. As a conductive object comes close and moves, its capacitance (to ground) will change accordingly.

The GW8316's Analog Front-End (AFE) circuit including Capacitance to Voltage Converter (CVC), Offset Cancellation DAC/High Resolution Oversampling ADC/Digital Signal Processing/Function, Timing & Calibration Control blocks co-works with MCU core to control and process capacitive proximity sensor data. Users can directly set each control register or simple register-based command can load preset values for each channel to registers. Users can turn on/off internal blocks in predefined settings or can directly turn on/off each block. Dedicated scan period controller block generates interrupts in defined periods on MCU for each channel. With these blocks, users can implement fully customized proximity sensing functionality in efficient ways.

The AFE handles the direct measurement and compensation of the sensor's capacitance and provide signals to the high-resolution oversampling analog to digital converter (ADC).

ADC translates it into a digital format. The digital processing block calculates the capacitance measurement received from the ADC and derives binary proximity status data, whether the distance to the object is over threshold or under threshold.

The control block initiates and adjust the AFE and the ADC operations like sampling rate, capacitance calibration, and send result data to memory via DMA or MCU core.

The GW8316 offers complete customization of sensor sensitivity, detection thresholds, and etc. Capacitive proximity detection relies on the internal gain and sampling frequency settings of the GW8316, as well as the size of the external sensor, to achieve optimal proximity detection distance. For example, to extend the proximity detection range without altering the capacitive sensor's dimensions, a high sensitivity setting and/or lower signal threshold setting for proximity detection can be used. GW8316 supports a command to load preset configuration for each channel directly.

### 10.4 Analog Front End (AFE)

### 10.4.1 Capacitance Sensing

Capacitive sensing involves detecting slight changes in capacitance within a noisy environment. As mentioned earlier, the proximity sensing interface of the GW8316 is based on capacitive sensing technology. In instances where the target conductive object (finger/palm/face, etc.) is absent, the sensor exclusively detects an inherent capacitance value, denoted as  $C_{\rm env}$ . This capacitance emerges due to the interaction of the sensor's electrical field with its environment, notably with ground regions. Upon the approach of the conductive object (finger/palm/face, etc.), the sensor's electric field experiences alteration, leading to a rise in the overall capacitance sensed by the sensor due to the user capacitance,  $C_{\rm user}$ .

$$C_{sensor} = C_{env} + C_{user}$$

The complexity in capacitive sensing lies in identifying the relatively minor change in  $C_{sensor}$  (with  $C_{user}$  typically accounting for only a small percentage). This differentiation must occur against the background of environmental noise ( $C_{env}$ ), which changes gradually alongside environmental factors like temperature. To address this, the GW8316 incorporates an capacitance compensation DAC. This DAC eliminates the  $C_{env}$  element on the circuit by extracting and processing solely the  $C_{user}$  component. This method leads to the highest level of robustness and efficiency.

### 10.4.2 CS Input and Active Shield Driver

### 10.4.3 AFE Block Diagram

The GW8316's AFE incorporates a Capacitance to Voltage Converter (CVC), responsible for sensing the sensor's capacitance and transforming it into a voltage signal for further processing. Additionally, it encompasses an offset compensation circuit, and a high-resolution oversampling ADC.

#### 10.4.4 Capacitance to Voltage Conversion (C-V)

The Capacitance to Voltage Converter interfaces capacitance and sample input in defined sampling frequency and generates voltage output. The sensitivity of the interface is predominantly established by the sampling frequency and gain parameter.

#### 10.4.5 Capacitance Compensation

Capacitance compensation involves conducting a singular measurement of  $C_{\text{env}}$ , which is then subtracted from the overall capacitance  $C_{\text{sensor}}$ . This was achieved by the capacitance compensation DAC removing the effect of  $C_{\text{env}}$  on CVC circuit. This action ensures that the ADC receives only the nearest contribution of  $C_{\text{user}}$ , effectively isolating it from  $C_{\text{sensor}}$ .

#### 10.4.6 Analog to Digital Conversion (ADC)

A high-resolution oversampling Analog-to-Digital Converter (ADC) is employed to transform the analog capacitance data into digital. Users can adjust the resolution of the ADC from 12 bit to 21 bit, which is affected by the setting of the Over-Sampling Ratio (OSR) of ADC. Be aware that the OSR and sampling frequency of ADC directly affect the bandwidth of the converted signal.

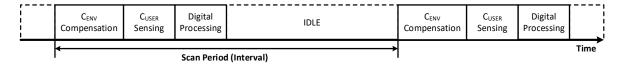

#### 10.4.7 Scan Period Controller

For power conservation and considering the inherently gradual occurrence of proximity events, the GW8316 supports to awaken periodically at a predefined scan interval. The scan period counter (SPC) block generates interrupts in user preset periods for each channel. There are 2 different period types which can be selected by simple register setting supporting users can implement Active/Doze Mode. The SPC is implemented with a dedicated lower power 128 kHz oscillator clock.

Users can freely implement environment compensation, proximity sensing and then put devices into idle state as depicted in the diagram below.

Figure 4 Sequencing of Proximity Sensing

The scan period establishes the minimum response time and can be programmed within the typical range of 0.5 ms to 32.768 s.

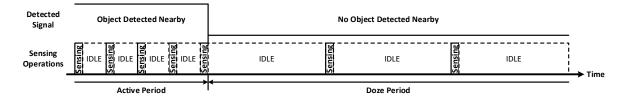

The reaction time of SAR detection is directly related to the scan period and inversely related to power consumption such that longer scan periods result in lower power consumption but also lead to longer detection reaction times. For example, users may implement the Active/Doze Mode Switching Concept like below. The GW8316 supports automatic period switching based on the detection result.

Figure 5 Active/Doze Mode Switching Scheme

### 10.5 Digital Signal Processing

The GW8316 includes dedicated high resolution digital signal processing (DSP) block which supports basic operations like ADD, SUBSTRACT, MULTIFLY, LEFT/RIGHT SHIFT, COPY, and COMPARE. The DSP block also supports more sophisticated operations like MAC OPERATION, AVERAGE, LOW PASS FILTER. Users can implement the user's own additional digital signal processing functions to enhance signal clarity or to extract additional information in real-time.

#### 10.6 Host Communication

The GW8316 supports two types of serial communication – I²C serial bus and UART. To notify data/information ready to the host in efficient ways, interrupt output on a PAD can be used with these. Various interrupt sources can be forwarded to the PAD output including sources from proximity sensing block like CONV\_DONE, COMP\_DONE, DETECT, etc. This makes it possible to reduce the host's resources usage for checking the proximity sensor periodically. I²C serial bus can operate solely in sleep mode. Hosts can wake up the GW8316 with a single I²C command.

Users may make the GW8316 response to host at various proximity conditions. These conditions include:

1. Close Detection (In Range): An interrupt can be triggered when the sensor detects that the user is in close proximity or within the defined range.

December 2, 2025 Gwanak Analog Page | 1 2

- 2. Far Detection (Out of Range): Alternatively, an interrupt can be triggered when the sensor detects that the user is far away and outside the designated range.

- 3. Both Close and Far Detection: In some cases, the interrupt can be configured to trigger for both close and far detection scenarios. This means that the interrupt can be activated when the user enters or exits the specified range.

An interrupt can serve another purpose as well—it can be triggered at the conclusion of every conversion within a scan period. This particular interrupt provides the host with a signal indicating that the proximity sensing block is actively in operation.

The host can leverage this signal for several purposes:

- 1. Synchronization of Noisy System Operations: In situations where the system's operations may introduce noise or timing uncertainties, the interrupt helps in synchronizing activities. By knowing when each conversion cycle is complete, the host can coordinate its actions with the sensing block more effectively, minimizing interference and ensuring reliable operation.

- 2. Synchronous Reading of Phase Data: The host can utilize this interrupt to read phase data (signal on different channels) synchronously. Synchronous reading ensures that the data is acquired at precisely the right moment, allowing the host to monitor and process proximity-related information accurately. This is particularly valuable for applications that demand real-time proximity data analysis and decision-making.

In summary, the interrupt serves as a synchronization tool, providing the host with a signal indicating the status of the proximity sensing block's conversions. This allows the host to manage system operations effectively, synchronize tasks, and access phase data in a synchronized manner for monitoring and control purposes.

In addition to the examples mentioned earlier, the interrupt functionality offers versatility by allowing mapping to various status bits, tailored to meet specific application requirements. One can refer to the register map for detailed information regarding how the interrupt can be customized and mapped to suit any needs of applications

#### 10.7 Power Controls

The GW8316 gives sufficient controllability to users to implement power/performance optimized characteristics. There are 5 power status defined in GW8316; Wait for Interrupt (WFI) #1, Wait for Interrupt (WFI) #2, IDLE, SLEEP, STOP, where wait for interrupt is the status MCU stops further instruction fetch or execution and just wait for an interrupt. Users can simply set PCON\_CMD to transit into required power status. When PCON\_CMD changes, block power control sequences are automatically performed.

#### **Power Modes**

| Power<br>State | MCU                      | MCU<br>CLOCK | SYSTEM<br>CLOCK | FLASH | 16 MHz<br>Oscillator | LDO         | 128 kHz<br>Oscillator |

|----------------|--------------------------|--------------|-----------------|-------|----------------------|-------------|-----------------------|

| WFI1           | Waiting for<br>Interrupt | On           | On              | On    | On                   | Normal Mode | On                    |

| WFI2           | Waiting for<br>Interrupt | Off          | On              | On    | On                   | Normal Mode | On                    |

| IDLE           | Waiting for<br>Interrupt | Off          | Off             | Off   | On                   | Normal Mode | On                    |

| SLEEP          | Waiting for<br>Interrupt | Off          | Off             | Off   | Off                  | Low Power   | On                    |

| STOP           | Waiting for<br>Interrupt | Off          | Off             | Off   | Off                  | Low Power   | Off                   |

### 10.8 I<sup>2</sup>C Interface

#### 10.8.1 Introduction

The I<sup>2</sup>C implementation of the GW8316, utilized by the host for communication, is:

- Two I<sup>2</sup>C interface: I<sup>2</sup>CO support master/slave mode, I<sup>2</sup>CS only support slave mode

- Standard (100kbps) and Fast (400kbps) modes

- 7-bit address, configurable by a resistor

- General call support

I<sup>2</sup>CS supports external wake-up. Because I<sup>2</sup>CS uses SCL as its clock, the host can wake-up the MCU core even when the internal oscillator is powered down in SLEEP or STOP mode. Whenever one byte is transferred by I<sup>2</sup>C bus, an interrupt is generated to the MCU core and the SCL is held low until the register is cleared.

Users can directly control generation of START/STOP condition, read/write data, and ACK generation. The  $GW8316~I^2C$  report various bus status like address matching, bus busy, etc. These functions enable users to implement customized protocols efficiently.

### 10.9 Registers

The following registers provide comprehensive scope for user-driven parameter customization. It's crucial to configure their values in alignment with the most recent application notes accessible (kindly consult your Gwanak Analog representative).

Please take note of the following:

- $\ ^{\square}$  Addresses not explicitly mentioned are reserved and should not undergo any writing operation.

- Any reserved bits should be retained at their default values unless explicitly directed otherwise.

- Unless specifically indicated otherwise, default values can be perceived as typical standards.

#### **SFR Registers**

| Resister Name         | R<br>W | Description       | Default | [7]         | [6] | [5] | [4]       | [3]       | [2]     | [1]        | [0]    |

|-----------------------|--------|-------------------|---------|-------------|-----|-----|-----------|-----------|---------|------------|--------|

| System Control Regist | ers    |                   |         |             |     |     |           |           |         |            |        |

| SP                    |        | Stack Pointer     | 0x07    |             |     |     |           |           |         |            |        |

| DPL                   |        | Data Pointer Low  | 0x00    |             |     |     | DPTF      | R[7:0]    |         |            |        |

| DPH                   |        | Data Pointer High | 0x00    |             |     |     | DPTR      | [15:8]    |         |            |        |

| SYSCON_AR             |        | System Authority  | 0x00    |             |     |     | А         | R         |         |            |        |

| SYSCON                |        | System Control    | 0x1D    | CPP_CTRL_EN | •   | •   | OSCLS_PDB | OSCHS_PDB | LDO_PDB | SUBLDO_PDB | CDB_EN |

| Resister Name | R<br>W | Description                                                                                                                                                                                                                                                             | Default | [7]           | [6]         | [5]  | [4]    | [3]      | [2]      | [1]              | [0]          |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|-------------|------|--------|----------|----------|------------------|--------------|

| SCCR          |        | System Clock Control                                                                                                                                                                                                                                                    | 0x0C    | 1             | PCLK_DIV_EN | ı    |        |          | SCLK_SEL | SCLK_SRC_DIV_DIS | SCLK_SRC_SEL |

| PCON          |        | Power Control  LDO_EN: "1" Do not power down LDO in SLEEP or STOP FLASH_EN: "1" Do not power down Flash in IDLE, SLEEP or STOP PCON_CMD: Power controller command 0: Wait for Interrupt 1 1: Wait for Interrupt 2 2: IDLE 3: SLEEP 4: STOP Others: Wait for Interrupt 1 | 0x00    |               | ,           | ,    | LDO_EN | FLASH_EN |          | PCON_CMD         |              |

| DPTR_BANK     | R<br>W | MCU DPTR Register Bank<br>Selection (Two Banks)                                                                                                                                                                                                                         | 0x00    | -             | -           | -    | -      | -        | -        | -                | MCU_DPTR     |

| XBANK         |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| XOFFSET       |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| PSW           |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| ACC           |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| В             |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| CMX           |        |                                                                                                                                                                                                                                                                         | 0x00    |               |             |      |        |          |          |                  |              |

| SUB_CLKEN_H   | R<br>W | Sub-block Clock Enable High                                                                                                                                                                                                                                             | 0x08    |               | ı           | PWM1 | PWM0   | I2CS     | 12C0     |                  | UART0        |

| SUB_CLKEN_L   | R<br>W | Sub-block Clock Enable Low                                                                                                                                                                                                                                              | 0x10    |               | AFEC        | DSP  | 5      | CRC      |          | ,                | ,            |

| SUB_RESET_H   | R<br>W | Sub-block Reset High                                                                                                                                                                                                                                                    | 0x00    |               |             | PWM1 | PWM0   | ISCS     | 12C0     | ı                | UARTO        |

| SUB_RESET_L   | R<br>W | Sub-block Reset Low                                                                                                                                                                                                                                                     | 0x00    |               | AFEC        | DSP  | FC     | CRC      | TIMER3   | TIMER1           |              |

| CHIPID_3      | R<br>O | CHIPID                                                                                                                                                                                                                                                                  | 0x00    | CHIPID[31:24] |             |      |        |          |          |                  |              |

| Resister Name       | R<br>W | Description                                                    | Default | [7]                   | [6]    | [5]   | [4]    | [3]               | [2]     | [1]    | [0]    |

|---------------------|--------|----------------------------------------------------------------|---------|-----------------------|--------|-------|--------|-------------------|---------|--------|--------|

| CHIPID_2            | R<br>O |                                                                | 0x83    |                       |        |       | CHIPIE | )[23:16           | []      |        |        |

| CHIPID_1            | R<br>O |                                                                | 0x10    |                       |        |       | CHIPII | D[15:8]           |         |        |        |

| CHIPID_0            | R<br>O |                                                                | 0xA0    |                       |        |       | CHIPI  | D[7:0]            |         |        |        |

| INTERRUPT Registers |        |                                                                |         |                       |        |       |        |                   |         |        |        |

| INT_OFFSET          | R<br>W | Interrupt Vector Base Address                                  | 0x00    |                       |        |       | IVS[   | 15:8]             |         |        |        |

| XINT_EDGE           | R<br>W | Ext interrupt, edge interrupt enable configuration for XINT[0] | 0x00    |                       |        | •     | NEG_EN |                   |         |        | POSEN  |

| XINT_SR             | R<br>W | Ext. interrupt status for XINT[0]                              | 0x00    |                       | 1      | 1     | NEG_ST |                   |         |        | POS_ST |

| IRQ0                | R<br>W | Interrupt Request 0                                            | 0x00    | •                     | •      | UART0 | AFEC   |                   | 12C0    | •      |        |

| IEN0                | R<br>W | Interrupt Enable 0                                             | 0x00    | INT_EN_GLOBAL         |        |       |        | INT_EN_LOCAL[6:0] |         |        |        |

| IP0                 | R<br>W | Interrupt Priority 0                                           | 0x00    | 0                     |        |       | INT_P  | RIORI"            | TY[6:0] |        |        |

| IRQ1                | R<br>W | Interrupt Request 1                                            | 0x00    | WDT                   | TIMER1 | 1     | ı      | I2CS              | EXT     | TIMER3 | ю      |

| IEN1                | R<br>W | Interrupt Enable 1                                             | 0x00    |                       |        | INT_  | _EN_L  | ]JAOC             | 14:7]   |        |        |

| IP1                 | R<br>W | Interrupt Priority 1                                           | 0x00    |                       |        | INT   | _PRIO  | RITY[1            | 4:7]    |        |        |

| IRQ2                | R<br>W | Interrupt Request 2                                            | 0x00    | SPC SPC DMA RX DMA TX |        |       |        |                   |         | PWM2   |        |

| IEN2                | R<br>W | Interrupt Enable 2                                             | 0x00    | INT_EN_LOCAL[22:15]   |        |       |        |                   |         | 1      |        |

| IP2                 | R<br>W | Interrupt Priority 2                                           | 0x00    | INT_PRIORITY[22:15]   |        |       |        |                   |         |        |        |

| ILEVEL              | R<br>W | Current Interrupt Level                                        | 0x00    | LEVEL[2:0             |        |       |        |                   |         | :0]    |        |

| Resister Name               | R<br>W | Description                                                       | Default | [7]                | [6]           | [5]     | [4]     | [3]     | [2]     | [1]     | [0]     |

|-----------------------------|--------|-------------------------------------------------------------------|---------|--------------------|---------------|---------|---------|---------|---------|---------|---------|

| GPIO Registers              |        |                                                                   |         |                    |               |         |         |         |         |         |         |

| P0                          | R<br>W | GPIO P07 ~ P00                                                    | 0x00    | P0<br>7            | P0<br>6       | P0<br>5 | P0<br>4 | P0<br>3 | P0<br>2 | P0<br>1 | P0<br>0 |

| P1                          | R<br>W | GPIO P17 ~ P10                                                    | 0x00    | P1<br>7            | P1<br>6       | P1<br>5 | P1<br>4 | P1<br>3 | P1<br>2 | P1<br>1 | P1<br>0 |

| I <sup>2</sup> C0 Registers |        |                                                                   |         |                    |               |         |         |         |         |         |         |

|                             | W      |                                                                   | 0x00    | STA                | STO           | RD      | WR      | ACK     |         |         | IACK    |

| I2C0_CSR                    | R      | I2C0 Command Status                                               | -       | RxACK              | TMOUT         | AL      | CMDF    | ADMF    | GCMF    | STDF    | 止       |

| I2C0_CTRL                   | W<br>R | I2C0 Control<br>I2C_EN, IEN: Write Only<br>BUSY, TOP: Read Only   | 0x00    | ISC_EN MASTER BUSY |               |         |         |         | TIP     |         |         |

| I2C0_PRER                   | R<br>W | I2C0 Pre-divider<br>I2C0 Freq. =<br>SCLK Freq. / (5 * (PRER + 1)) | 0x00    |                    |               |         | PR      | RER     |         |         | 1       |

| I2C0_ADDR                   | R<br>W | I2C0 Device Address                                               | 0x00    |                    |               | D       | EVADI   | OR      |         |         | GC      |

| I2C0_DR                     | R<br>W | I2C0 Data                                                         | 0x00    |                    |               |         | DA      | ATA     |         |         |         |

| I2C0_TOR                    | R<br>W | I2C0 Time-out Value                                               | 0x00    |                    |               |         | TO      | OR      |         |         |         |

| I2CS_CSR                    | W      | I2CS Command and Status                                           | 0x00    |                    |               |         |         |         |         |         | IACK    |

| 1200_001                    | R      | 1200 Command and Status                                           | 0x00    | RXACK              |               |         | BDF     | ADMF    | GCMF    | STDF    |         |

| I2CS_ADDR                   | R<br>W | I2CS Slave Address                                                | 0x40    |                    |               | SL      | .V_ADI  | DR      |         |         | GC      |

| I2CS_CFG                    | R<br>W | I2CS Configuration                                                | 0x7F    | -                  | STRETCH_RLAST | WE_BDF  | WE_ADMF | WE_STDF | IE_BDF  | IE_ADMF | IE_STDF |

| I2CS_DR                     | R<br>W | I2CS Data                                                         | 0x00    | DATA               |               |         |         |         |         |         |         |

| Resister Name | R<br>W | Description              | Default | [7]    | [6]  | [5]  | [4]         | [3]     | [2]      | [1]  | [0]      |  |  |

|---------------|--------|--------------------------|---------|--------|------|------|-------------|---------|----------|------|----------|--|--|

| I2CS_SDA_DLY  | R<br>W | I2CS Delay Configuration | 0x00    | -      | -    | -    | -           |         | SUA_CULY |      | SDA_IDLY |  |  |

| PWM Registers |        |                          |         |        |      |      |             |         | ,,       |      |          |  |  |

| PWM0_PRED     | R<br>W | PWM0 Pre-divider         | 0x00    | INTDIS | MEAS |      | PRED[5:0]   |         |          |      |          |  |  |

| PWM0_PLSPL    | R<br>W | PWM0 Pulse Period        | 0x00    |        |      |      | PLSF        | P[7:0]  |          |      |          |  |  |

| PWM0_MODE     | R<br>W | PWM0 Mode                | 0x00    | N<br>N | OPOL | MODE |             | Pl      | _SP[12   | ::8] |          |  |  |

| PWM0_PLSW1L   | R<br>W | PWM0 Pulse Width 1       | 0x00    |        |      |      | PLSW        | /1[7:0] |          |      |          |  |  |

| PWM0_PLSW1H   | R<br>W | PWM0 Pulse Width 1       | 0x00    | -      | -    | -    |             | PL      | SW1[1    | 2:8] |          |  |  |

| PWM0_PLSW2L   | R<br>W | PWM0 Pulse Width 2       | 0x00    |        |      | 1    | PLSW        | /2[7:0] |          |      |          |  |  |

| PWM0_PLSW2H   | R<br>W | PWM0 Pulse Width 2       | 0x00    | -      | -    | -    |             | PL      | SW2[1    | 2:8] |          |  |  |

| PWM1_PRED     | R<br>W | PWM1 Pre-divider         | 0x00    | INTDIS | MEAS |      |             | PRE     | D[5:0]   |      |          |  |  |

| PWM1_PLSPL    | R<br>W | PWM1 Pulse Period        | 0x00    |        |      | ı    | PLSF        | P[7:0]  |          |      |          |  |  |

| PWM1_MODE     | R<br>W | PWM1 Mode                | 0x00    | Z<br>U | OPOL | MODE |             | Pl      | _SP[12   | ::8] |          |  |  |

| PWM1_PLSW1L   | R<br>W | PWM1 Pulse Width 1       | 0x00    |        |      | ı    | PLSW        | /1[7:0] |          |      |          |  |  |

| PWM1_PLSW1H   | R<br>W | PWM1 Pulse Width 1       | 0x00    | -      | -    | -    |             | PL      | SW1[1    | 2:8] |          |  |  |

| PWM1_PLSW2L   | R<br>W | PWM1 Pulse Width 2       | 0x00    |        |      |      | PLSW        | /2[7:0] |          |      |          |  |  |

| PWM1_PLSW2H   | R<br>W | PWM1 Pulse Width 2       | 0x00    | -      | -    | -    | PLSW2[12:8] |         |          |      |          |  |  |

| DSP Registers |        |                          |         |        |      |      |             |         |          |      |          |  |  |

| DSP_CON       | W      | DSP Control              | -       | ı      | ı    | ı    |             |         |          |      |          |  |  |

|                | Г      | Γ                        |         |                                   |         |     |          |          |         |         |               |

|----------------|--------|--------------------------|---------|-----------------------------------|---------|-----|----------|----------|---------|---------|---------------|

| Resister Name  | R<br>W | Description              | Default | [7]                               | [6]     | [5] | [4]      | [3]      | [2]     | [1]     | [0]           |

|                | R      |                          | 0x08    | BUSY                              | 0       | 0   | 0        | ADD_ZERO | ADD_NEG | ADD_POS | 3             |

| DSP_CMD        | R<br>W | DSP Command              | 0x00    |                                   | OP_CODE |     | YSEL     | ZSTORE   |         |         |               |

| DSP_DPTR       | R<br>W | DSP DMA Bank Selection   | 0x00    | DPTR_                             |         |     |          |          |         |         |               |

| DSP_SHIFT      | R<br>W | DSP Shift Amount         | 0x00    | , , ES                            |         |     |          |          |         |         |               |

| DSP_DWIDTH     | R<br>W | DSP Data Width           | 0x15    | , , KEN X                         |         |     |          |          | √_LEN   |         | 7<br>_<br>LEN |

| DSP_XPTR       | R<br>W | DSP Operand X Pointer    | 0x00    |                                   |         |     | PTR[7:1] |          |         |         | XCONST        |

| DSP_YPTR       | R<br>W | DSP Operand Y Pointer    | 0x00    |                                   |         |     | PTR[7:1] |          |         |         | YCONST        |

| DSP_ZPTR       | R<br>W | DSP Result Z Pointer     | 0x00    |                                   |         |     | PTR[7:1] |          |         |         | 0             |

| UART Registers |        |                          | I       |                                   |         |     |          |          |         |         |               |

| UART0_CSR      | R<br>W | UART0 Control and Status | 0x00    | EN PS PS SL                       |         |     |          |          | TX_BRK  | ABRE    |               |

| UART0_ISR      | R<br>W | UART0 Interrupt Status   | 0x00    | SYNCDET TF_EMPTY RF_FULL RF_READY |         |     | BRKDET   | ЬЕ       | 뮢       | OVR     |               |

| UART0_IBRD     | R<br>W | UART0 Baud Rate Divider  | 0x00    | PCLK_SEL CLK_DIV                  |         |     |          |          | 1       |         |               |

| Resister Name   | R<br>W | Description                                                           | Default | [7]       | [6]       | [5]      | [4]      | [3]              | [2]        | [1]     | [0]     |

|-----------------|--------|-----------------------------------------------------------------------|---------|-----------|-----------|----------|----------|------------------|------------|---------|---------|

| UART0_DR        | R<br>W | TX/RX Data                                                            | 0x00    |           |           |          | DA       | ATA              |            |         |         |

| UART0_FBRD      | R<br>W | Fractional Baud Rate Divider                                          | 0x00    |           |           |          | FBRI     | D[7:0]           |            |         |         |

| TIMER Registers |        |                                                                       | I       |           |           |          |          |                  |            |         |         |

| T1MR            | R<br>W | Timer1 Mode Control                                                   | 0x00    |           | P         | CLK_S    | EL       |                  | RD_CNT     | ME      | EN      |

| T1RL            | R<br>W | Timer1 Time                                                           | 0x00    |           |           |          | T1R      | [7:0]            | ı          | ı       |         |

| T1RH            | R<br>W | Timer1 Time                                                           | 0x00    |           |           |          |          |                  |            |         |         |

| WDTMR           | R<br>W | Watch Dog Timer Mode                                                  | 0x00    |           |           | PCLK_SEL |          | CLK              | RESET      | Z<br>W  |         |

| WDTR            | R<br>W | Watch Dog Timer Time                                                  | 0x00    |           |           |          |          |                  |            |         |         |

| T3MR            | R<br>W | Timer3 Mode Control                                                   | 0x00    |           | P         | CLK_S    | EL       |                  | RD_CNT     | ME      | EN      |

| T3RL            | R<br>W | Timer3 Time                                                           | 0x00    |           |           |          | T3R      | [7:0]            | ı          |         |         |

| T3RH            | R<br>W | Timer3 Time                                                           | 0x00    |           |           |          | T3R      | [15:8]           |            |         |         |

| SPC Registers   |        |                                                                       | I       |           |           |          |          |                  |            | I       |         |

| SPC_CSR         | R<br>W | Scan Period Control and Status                                        | 0x00    | INT_STATE | PAUSE_CDC | EN_CDC   | MATCH_BW | N<br>H<br>L<br>N | INT_ON_GSP | PAUSE   | Z       |

|                 | R      | If MATCH_BW=0, Scan Period<br>Expiration Status of Each<br>Channel    | 0x00    | -         | -         | CH<br>5  | CH<br>4  | CH<br>3          | CH<br>2    | CH<br>1 | CH<br>0 |

| SPC_MATCH       | R      | If MATCH_BW=1, Scan Period<br>Expiration Status of Current<br>Channel | 0x00    |           |           |          |          |                  |            | -       | МАТСН   |

| CRC Registers   |        |                                                                       |         |           |           |          |          |                  |            |         |         |

| CRC_CON         | R<br>W | CRC Control                                                           | 0x00    |           | TAR       | GET      |          | TY               | PΕ         | 0       | EN      |

| CRC_DIN         | R<br>W | CRC Data                                                              | 0x00    | DIN[7:0]  |           |          |          |                  |            |         |         |

| Resister Name | R<br>W | Description | Default | [7]       | [6] | [5] | [4] | [3] | [2] | [1] | [0] |

|---------------|--------|-------------|---------|-----------|-----|-----|-----|-----|-----|-----|-----|

| CRC_L         | R<br>W | CRC Low     | 0x00    | CRC[7:0]  |     |     |     |     |     |     |     |

| CRC_H         | R<br>W | CRC High    | 0x00    | CRC[15:8] |     |     |     |     |     |     |     |

### XSFR Registers

| Resister Name  | R<br>W | Description                                       | Default | [7]     | [6]     | [5]     | [4]     | [3]     | [2]     | [1]     | [0]     |

|----------------|--------|---------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| GPIO Registers |        |                                                   |         |         |         |         |         |         |         |         |         |

| P0PINMUX_H     | R<br>W | GPIO Port 0 Pinumx P07 ~ P04                      | 0x50    | P       | 07      | P       | 06      | P       | 05      | P       | 04      |

| P0PINMUX_L     | R<br>W | GPIO Port 0 Pinumx P03 ~ P00                      | 0x00    | P       | 03      | Р       | 02      | P       | 01      | P       | 00      |

| P1PINMUX_H     | R<br>W | GPIO Port 1 Pinumx P17 ~ P14                      | 0x00    | P       | 17      | Р       | 16      | Р       | 15      | P       | 14      |

| P1PINMUX_L     | R<br>W | GPIO Port 1 Pinumx P13 ~ P10                      | 0x00    | P       | 13      | Р       | 12      | Р       | 11      | Р       | 10      |

| P0_DS_H        | R<br>W | GPIO Port 0 Driving Strength<br>Control P07 ~ P04 | 0xAA    | P       | 07      | P       | 06      | P       | 05      | P       | 04      |

| P0_DS_L        | R<br>W | GPIO Port 0 Driving Strength<br>Control P03 ~ P00 | 0xAA    | P       | 03      | P       | 02      | P       | 01      | P       | 00      |

| P1_DS_H        | R<br>W | GPIO Port 0 Driving Strength<br>Control P17 ~ P14 | 0x00    |         | -       |         | -       |         | -       |         | -       |

| P1_DS_L        | R<br>W | GPIO Port 0 Driving Strength<br>Control P13 ~ P10 | 0x0A    |         | -       |         | -       | Р       | 11      | Р       | 10      |

| P0_DIR         | R<br>W | GPIO Port 0 direction control                     | 0x00    | P0<br>7 | P0<br>6 | P0<br>5 | P0<br>4 | P0<br>3 | P0<br>2 | P0<br>1 | P0<br>0 |

| P1_DIR         | R<br>W | GPIO Port 1 direction control                     | 0x00    | P1<br>7 | P1<br>6 | P1<br>5 | P1<br>4 | P1<br>3 | P1<br>2 | P1<br>1 | P1<br>0 |

| P0_PE          | R<br>W | GPIO Port 0 pull-up/down enable                   | 0x00    | P0<br>7 | P0<br>6 | P0<br>5 | P0<br>4 | P0<br>3 | P0<br>2 | P0<br>1 | P0<br>0 |

| P1_PE          | R<br>W | GPIO Port 1 pull-up/down enable                   | 0x02    | P1<br>7 | P1<br>6 | P1<br>5 | P1<br>4 | P1<br>3 | P1<br>2 | P1<br>1 | P1<br>0 |

| P0_PS          | R<br>W | GPIO Port 0 pull-up/down selection                | 0x00    | P0<br>7 | P0<br>6 | P0<br>5 | P0<br>4 | P0<br>3 | P0<br>2 | P0<br>1 | P(<br>0 |

| P1_PS          | R<br>W | GPIO Port 1 pull-up/down selection                | 0x00    | P1<br>7 | P1<br>6 | P1<br>5 | P1<br>4 | P1<br>3 | P1<br>2 | P1<br>1 | P1<br>0 |

| P0_DB          | R<br>W | GPIO Port 0 Debounce Filter on/off control        | 0x03    | P0<br>7 | P0<br>6 | P0<br>5 | P0<br>4 | P0<br>3 | P0<br>2 | P0<br>1 | P(      |

| P1_DB          | R<br>W | GPIO Port 1 Debounce Filter on/off control        | 0x00    | P1<br>7 | P1<br>6 | P1<br>5 | P1<br>4 | P1<br>3 | P1<br>2 | P1<br>1 | P1<br>0 |

| P0_DB_CNT      | R<br>W | GPIO Port 0 Debounce Filter<br>Count Value        | 0x02    | -       | -       | -       | -       |         | DB_     | CNT     |         |

| P1_DB_CNT      | R<br>W | GPIO Port 0 Debounce Filter<br>Count Value        | 0x02    | -       | -       | -       | -       |         | DB_     | CNT     |         |

| Resister Name   | R<br>W | Description                                                                                                                                                                                                                         | Default | [7]      | [6] | [5] | [4]           | [3]    | [2]     | [1]       | [0]   |  |

|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-----|-----|---------------|--------|---------|-----------|-------|--|

| SEL_CAPTURE     | R      | Select Timer 1/3 Capture Signal Source SEL1: capture signal source for Timer 1, 0 – disable, 1 - P0[2], 2 – P[5], 3 – P[6] SEL3: capture signal source for Timer3, 0-disable, 1-P1[0], 2-OSCHS divided pulse, 3-OSCLS divided pulse | 0x00    | -        | -   | -   | -             | SE     | EL3     | SE        | EL1   |  |

| PIN_XCHG        | R<br>W | Pin Exchange Control UART0: '1' exchanges UART_RXD/UART_TXD I2C0: '1' exchanges I2C0 SCL0/SDA0 I2CS: '1' exchanges I2CS SSCL/SSDA T1P1: '1' exchanges TIMER1_O/PWM01_IO outputs P11OSC: '1' exchanges PWM11_IO/OSCLS_O outputs      | 0x00    | -        | -   | -   | P110SC        | T1P01  | I2CS    | 12C0      | UARTO |  |

| DMA Registers   |        |                                                                                                                                                                                                                                     |         |          |     |     |               |        |         |           |       |  |

| DMA_CH2_SRC_H   | R<br>W | DMA Channel2 Source Address<br>High Bits                                                                                                                                                                                            | 0x00    | -        | -   |     | SRC_PTR[13:8] |        |         |           |       |  |

| DMA_CH2_SRC_L   | R<br>W | DMA Channel2 Source Address<br>Low Bits                                                                                                                                                                                             | 0x00    |          |     |     | SRC_PTR[7:0]  |        |         |           |       |  |

| DMA_CH2_TX_CTRL | R<br>W | DMA Channel2 TX Control                                                                                                                                                                                                             | 0x00    | C_DMA_GO |     |     | C_N_1         | MINUS  | _1[6:0] |           |       |  |

| DMA_CH2_TXSEL   | R<br>W | DMA Channel2 TX Select                                                                                                                                                                                                              | 0x00    | -        | -   | -   | -             | -      | -       | TX_<br>[1 |       |  |

| DMA_CH2_DST_H   | R<br>W | DMA Channel2 Destination<br>Address High Bits                                                                                                                                                                                       | 0x00    | -        | -   |     |               | ST_P   | TR[13:  | 8]        |       |  |

| DMA_CH2_DST_L   | R<br>W | DMA Channel2 Destination<br>Address Low Bits                                                                                                                                                                                        | 0x00    |          | 1   | ļ   | DST_P         | TR[7:0 | )]      |           |       |  |

| DMA_CH2_RXCTRL  | R<br>W | DMA Channel2 RX Control                                                                                                                                                                                                             | 0x00    | C_DMA_GO |     |     | C_N_1         | MINUS  | _1[6:0] |           |       |  |

| DMA_CH2_RXSEL   | R<br>W | DMA Channel2 RX Select                                                                                                                                                                                                              | 0x00    | -        | -   | -   | -             | -      | -       | RX_<br>[1 |       |  |

| PWM Registers   |        |                                                                                                                                                                                                                                     |         |          |     |     |               |        |         |           |       |  |

| PWM_PLSW1_H     | R<br>O | DWM1 input pulse width                                                                                                                                                                                                              | -       |          | 0   |     |               | WI     | DTH[1   | 2:8]      |       |  |

| PWM_PLSW1_L     | R<br>O | PWM1 input pulse width                                                                                                                                                                                                              | -       |          |     |     | WIDT          | H[7:0] |         |           |       |  |

| PWM_PLSW2_H     | R<br>O | DIMMO input puls                                                                                                                                                                                                                    | -       |          | 0   |     |               | WI     | DTH[1   | 2:8]      |       |  |

| PWM_PLSW2_L     | R<br>O | PWM2 input pulse width                                                                                                                                                                                                              | -       |          |     |     | WIDT          | H[7:0] |         |           |       |  |

| PWM_PLSW3_H     | R<br>O | PWM3 input pulse width                                                                                                                                                                                                              | -       |          | 0   |     |               | WI     | DTH[1   | 2:8]      |       |  |